содержание .. 7 8 9 10 ..

Полупроводники. Каталог (2011 год) - часть 9

SN75468, SN75469

DARLINGTON TRANSISTOR ARRAYS

SLRS023B – DECEMBER 1976 – REVISED SEPTEMBER 1995

3–5

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

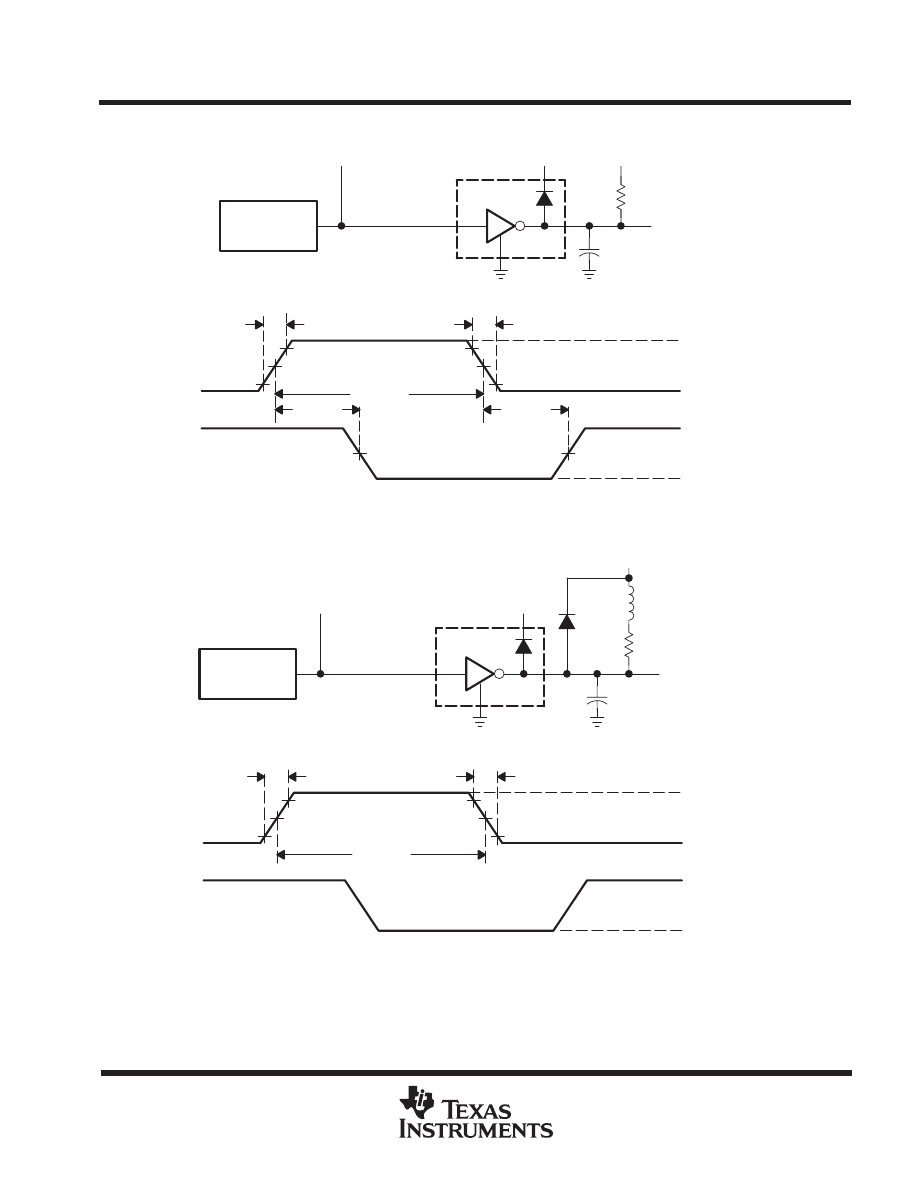

PARAMETER MEASUREMENT INFORMATION

Input

Open

VS = 50 V

RL = 163

Ω

Output

CL = 15 pF

(see Note B)

90%

90%

50%

50%

10%

10%

50%

50%

tPHL

tPLH

0.5

µ

s

≤

10 ns

≤

5 ns

VIH

(see Note C)

0 V

VOH

VOL

Input

Output

TEST CIRCUIT

VOLTAGE WAVEFORMS

Pulse

Generator

(see Note A)

Figure 9. Test Circuit and Voltage Waveforms

Input

Open

VS

200

Ω

Output

CL = 15 pF

(see Note B)

90%

90%

1.5 V

1.5 V

10%

10%

40

µ

s

≤

10 ns

≤

5 ns

VIH

(see Note C)

0 V

VOH

VOL

Input

Output

TEST CIRCUIT

VOLTAGE WAVEFORMS

1N3064

2 mH

Pulse

Generator

(see Note A)

Figure 10. Latch-Up Test Circuit and Voltage Waveforms

NOTES: A. The pulse generator has the following characteristics: PRR = 12.5 kHz, ZO = 50

Ω

.

B. CL includes probe and jig capacitance.

C. For testing the ’468, VIH = 3 V; for the ’469, VIH = 8 V.