содержание .. 4 5 6 7 ..

Полупроводники. Каталог (2011 год) - часть 6

12/26

¡ Semiconductor

MSM82C51A-2RS/GS/JS

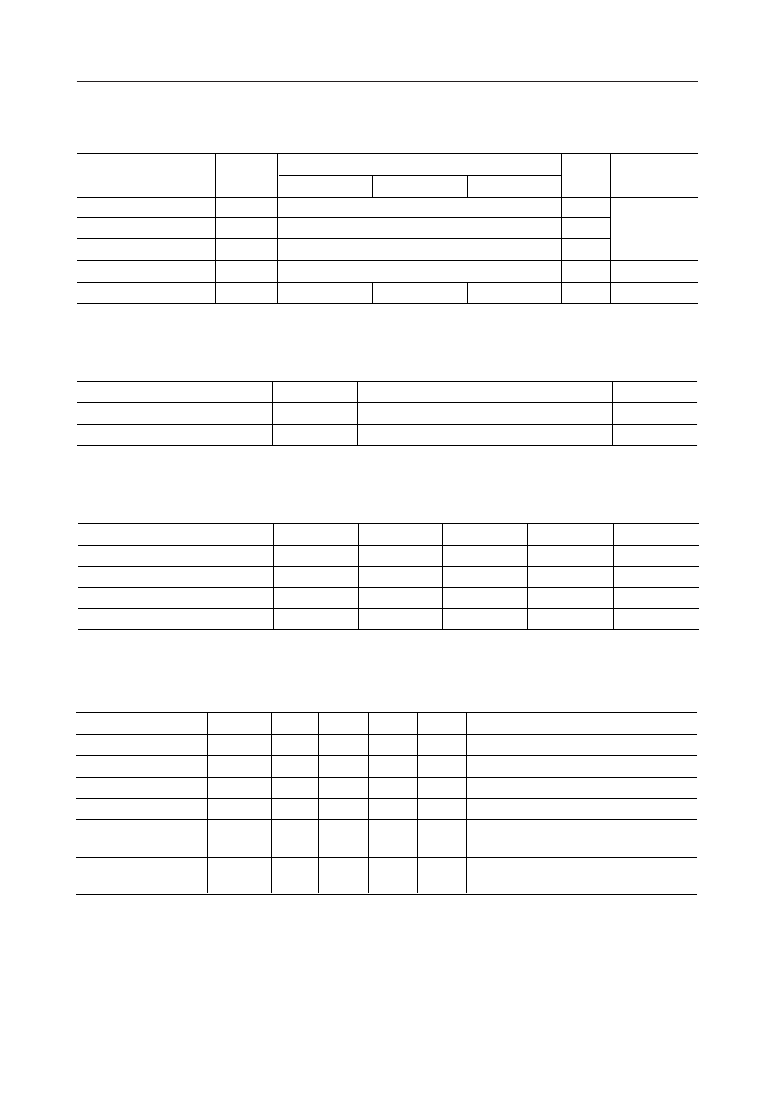

ABSOLUTE MAXIMUM RATING

–55 to +150

MSM82C51A-2RS

Power Supply Voltage

V

CC

–0.5 to +7

V

Input Voltage

V

IN

–0.5 to V

CC

+0.5

V

Output Voltage

V

OUT

–0.5 to V

CC

+0.5

V

Storage Temperature

T

STG

°C

Power Dissipation

P

D

0.7

W

Parameter

Unit

Symbol

With respect

to GND

—

Ta = 25°C

Conditions

Rating

MSM82C51A-2GS MSM82C51A-2JS

0.9

0.9

OPERATING RANGE

Range

Power Supply Voltage

V

CC

3 - 6

V

Operating Temperature

T

op

–40 to 85

°C

Parameter

Unit

Symbol

RECOMMENDED OPERATING CONDITIONS

DC CHARACTERISTICS

Typ.

Max.

"L" Output Voltage

V

OL

—

0.45

V

"H" Output Voltage

V

OH

—

—

V

Parameter

Unit

Symbol

Min.

—

3.7

I

OL

= 2.5 mA

I

OH

= –2.5 mA

Measurement Conditions

Input Leak Current

I

LI

—

10

m

A

Output Leak Current

I

LO

—

10

m

A

–10

–10

0

£

V

IN

£

V

CC

0

£

V

OUT

£

V

CC

Operating Supply

Current

—

5

mA

—

Asynchronous X64 during Transmitting/

Receiving

Standby Supply

Current

—

100

m

A

—

I

CCO

I

CCS

All Input voltage shall be fixed at V

CC

or

GND level.

(V

CC

= 4.5 to 5.5 V Ta = –40°C to +85°C)

Typ.

Power Supply Voltage

V

CC

5

V

T

op

+25

"L" Input Voltage

V

IL

—

"H" Input Voltage

V

IH

—

Min.

4.5

–40

–0.3

2.2

Max.

5.5

+85

+0.8

V

CC

+0.3

Parameter

Unit

Symbol

°C

V

V

Operating Temperature